# S-Band, GaN/SiC, RF Power Amplifier Pallet

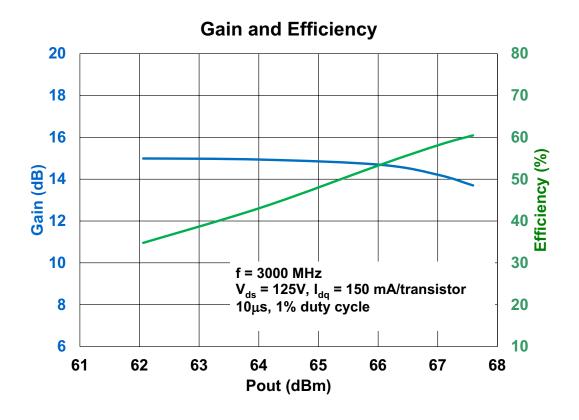

3.0 GHz  $\mid$  5500W  $\mid$  60 % Efficiency typ  $\mid$  14.2 dB Gain typ  $\mid$  125 V  $\mid$  10 $\mu$ s Pulse Length, 1% Duty Cycle

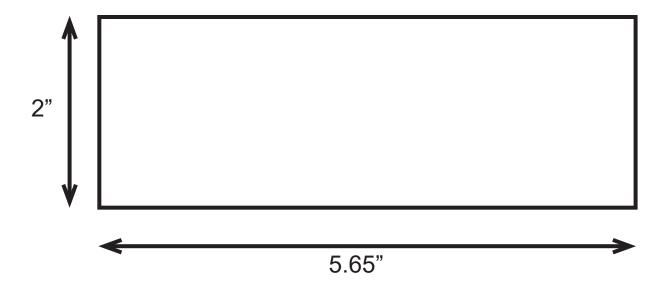

Introducing IGNP3000S5000, the pinnacle of S-Band power amplifier pallets available today. Powered by Integra's Gen4 GaN/SiC, IGNP3000S5000 delivers an astonishing 5500W of peak output power and boasts a typical power gain of 14dB at an impressive 60% drain efficiency, all within a compact 2" x 5.6" form factor. This powerhouse of innovation is designed for practicality and efficiency, enabling replacement of traditional vacuum electron device (VED) based amplifier systems with ease, even at megawatt power levels. Experience unparalleled improvements in system size, weight, power, cost, and complexity, paving the way for the next generation of RF amplifier system performance. Elevate your system architecture with IGNP3000S5000 and witness the future of high-performance system amplification.

#### **FEATURES**

- ✓ Unmatched Power Density: Experience an incredible 491W/in², setting a new standard in amplifier power.

- ✓ Solid-State Excellence: Effortlessly replace VEDs with cutting-edge solid-state technology.

- Advanced GaN/SiC Technology: Powered by Integra's Gen4 GaN/SiC for superior performance.

- ✓ Impressive Efficiency: Achieve a remarkable 60% drain efficiency for optimal operation.

- ✓ Unbeatable Output Power: Delivering 500% more output power than competitors.

- ✓ Streamlined Design: Replace multiple legacy amplifiers with a single, powerful unit.

- ✓ Innovative Architecture: Eliminate complex power combining layers in your amplifier system.

- ✓ Compact Form Factor: All this power in a sleek 2" x 5.6" pallet form factor.

- $\checkmark$  Seamless Integration: 50 $\Omega$  matched input and outputs for easy integration.

## **APPLICATIONS**

Particle Accelerators and ISM Systems

Table 1. RF Electrical Characteristics (Case temperature = 30 °C unless otherwise stated)

| Parameter               | Symbol   | Min | Тур  | Max | Units | Test Conditions                                                                     |

|-------------------------|----------|-----|------|-----|-------|-------------------------------------------------------------------------------------|

| Gain                    | G        |     | 14.2 |     | dB    |                                                                                     |

| Drain Efficiency        | η        |     | 58   |     | %     | P <sub>OUT</sub> = 5000W                                                            |

| Pulse Droop             | D        |     | -0.1 |     | dB    | f = 3.0 GHz                                                                         |

| Input Return Loss       | IRL      |     | 24   |     | dB    | 10 $\mu$ s pulse length, 1% duty cycle $V_{DS} = 125V$ , $I_{DS} = 150$ mA per side |

| VSWR Mismatch Stability | VSWR-S   | 2:1 |      |     |       |                                                                                     |

| VSWR Withstand          | VSWR-LMT | 5:1 |      |     |       |                                                                                     |

Note: Consult Integra Technologies Application Note 001 for information on how RF output power and pulse droop are measured.

**Table 2. Absolute Maximum Ratings (Not Simultaneous)**

| Parameter                     | Symbol              | Value       | Units | Test Conditions |

|-------------------------------|---------------------|-------------|-------|-----------------|

| DC Drain-Source Voltage       | V <sub>DS</sub>     | 350         | V     | 25 °C           |

| DC Gate-Source Voltage        | V <sub>GS</sub>     | -8 to +1    | V     | 25 °C           |

| DC Drain Current per side     | I <sub>D</sub>      | 72          | А     | 25 °C           |

| DC Gate Current per side      | I <sub>G</sub>      | 14.4        | mA    | 25 °C           |

| RF Input Power                | $P_{RF,IN}$         | 225         | W     | 25 °C           |

| Operating Channel Temperature | T <sub>ch</sub>     | -55 to +225 | °C    |                 |

| Storage Temperature           | T <sub>stg</sub>    | -55 to +150 | °C    |                 |

| Soldering Temperature         | T <sub>SOLDER</sub> | 260 for 60s | °C    |                 |

Note: Operation outside the limits given in this table may cause permanent damage to the transistor

Table 3. DC Electrical Characteristics (Case temperature = 25 °C unless otherwise stated)

| Parameter              | Symbol         | Min  | Тур  | Max | Units | Test Conditions                              |

|------------------------|----------------|------|------|-----|-------|----------------------------------------------|

| Gate Pinch-Off Voltage | V <sub>P</sub> | -5.0 |      |     | V     | $V_{DS} = 125V, I_{DS} = 1mA$                |

| Quiescent Gate Voltage | V <sub>Q</sub> |      | -4.0 |     | V     | $V_{DS} = 125V$ , $I_{DS} = 150$ mA per side |

Table 4. Thermal Resistance (Case temperature = 30 °C unless otherwise stated)

| Parameter                                   | Symbol          | Min | Тур   | Max | Units | Test Conditions                                                                         |

|---------------------------------------------|-----------------|-----|-------|-----|-------|-----------------------------------------------------------------------------------------|

| Peak Thermal Resistance,<br>Channel to Case | R <sub>TH</sub> |     | 0.044 |     | °C/W  | $P_{diss} = 1570W$ per transistor $10\mu s$ pulse length, 1% duty cycle $V_{DS} = 125V$ |

## **TYPICAL PERFORMANCE**

Figure 1

## **DIMENSIONS**

#### **ESD Rating**

| Parameter                       | Rating               | Standard               |  |  |

|---------------------------------|----------------------|------------------------|--|--|

| ESD Human Body Model (HBM)      | TBD                  | ESDA/JEDEC JS-001-2012 |  |  |

| ESD Charged Device Model (CDM)  | TBD                  | JEDEC JESD22-C11F      |  |  |

| Moisture Sensitivty Level (MSL) | Unlimited Shelf Life | IPC/JEDEC J-STD-020    |  |  |

## **RoHS Compliance**

Integra Technologies, Inc declares that its GaN and LDMOS Transistor Products comply with EU Directive 2011/65/EU on the restriction of the use of certain hazardous substances in electrical and electronic equipment (RoHS2), as adopted by EU member states on January 2, 2013 and amended on March 31, 2015 by EU Directive 2015/863/EU.

## **REACH Compliance**

Integra Technologies supports EU Regulation number 1907/2006 concerning the Registration, Evaluation, Authorization, and Restriction of Chemicals (REACH) as these apply to Integra semiconductor products, development tools, and shipping packaging.

In support of the REACH regulation, Integra will:

- •Inform customers and recipients of Integra product if they contain any substances that are of very high concern (SVHC) per the European Chemical Agency (ECHA) website.

- •Notify ECHA if any Integra product that contains any SVHCs which exceed guidelines for REACH chemicals by weight per part number and for total content weight per year for all products produced in or imported to the European market.

- Cease shipments of product containing REACH Annex XIV substances until authorization has been obtained.

- Cease shipment of product containing REACH Annex XVII chemicals when restrictions apply.

Integra has evaluated its materials, BOMs, and product specifications and product and has determined that this transistor conforms to all REACH and SVHC regulations and guidelines. Integra has implemented actions and control programs that will assure continued compliance.

### Disclaimer

Integra Technologies Inc. reserves the right to make changes without further notice to any products herein. Integra Technologies Inc. makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Integra Technologies Inc. assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Integra Technologies Inc. products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Integra Technologies Inc. customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Integra Technologies Inc. for any damages resulting from such improper use or sale.

DEFINITIONS:

DATA SHEET STATUS

Advanced Specification - This data sheet contains Advanced specifications.

Preliminary Specification - This data sheet contains specifications based on preliminary measurements and data.

Final Specification - This data sheet contains final product specifications.

MAXIMUM RATINGS Stress above one or more of the maximum ratings may cause permanent damage to the device. These are maximum ratings only operation of the device at these or at any other conditions above those given in the characteristics sections of the specification is not implied. Exposure to maximum values for extended periods of time may affect device reliability.

Integra Technologies, 321 Coral Circle, El Segundo, CA 90245-4620 | Phone: 310-606-0855 | Fax: 310-606-0865